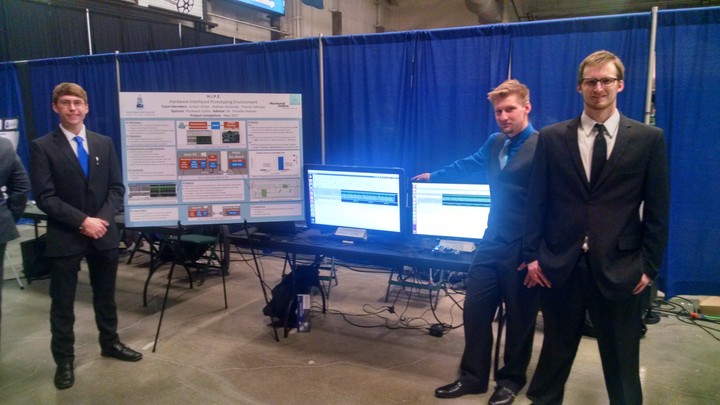

HIPE Team at Engineering Expo

HIPE Team at Engineering ExpoAbstract

Digital hardware designers currently utilize software simulation tools to prototype and verify their digital designs. Existing tools provide designers with accurate signal information that allows them to identify and amend errors in their designs. Simulations for digital hardware designs can take days to complete; this costs companies, such as Rockwell Collins, over $100,000 per engineer per year! Steadily changing markets demand increasingly complex designs to meet customer needs and keep up with rapidly advancing technology. Complex designs are developed using iterative prototyping and require a significant amount of processing power to verify using software simulations. Since these designs are modeled and processed by a CPU onboard a PC, the computation time required to analyze millions of events becomes impractical. Rapid design prototyping is an essential part of the digital hardware design process. For this reason, the project will build on the pre-existing industry standard workflow used by Rockwell Collins in order to allow digital designers to interact with signals from complex digital designs in the same way that they would in the current simulation environment.

The goal of this project is to decrease simulation time by integrating hardware with the existing simulation environment while still providing access to internal signals of a design under test. A Hardware Integrated Prototyping Environment (HIPE) is being developed to overcome the existing simulation software’s shortcomings. The HIPE design consists of an FPGA development board, the existing simulation software on a PC, and a hardware-software interface connecting the two.